3나노 시대, 반도체는 왜 점점 ‘이상해질까?

💻 3나노 시대, 반도체는 왜 점점 ‘이상해질까?’

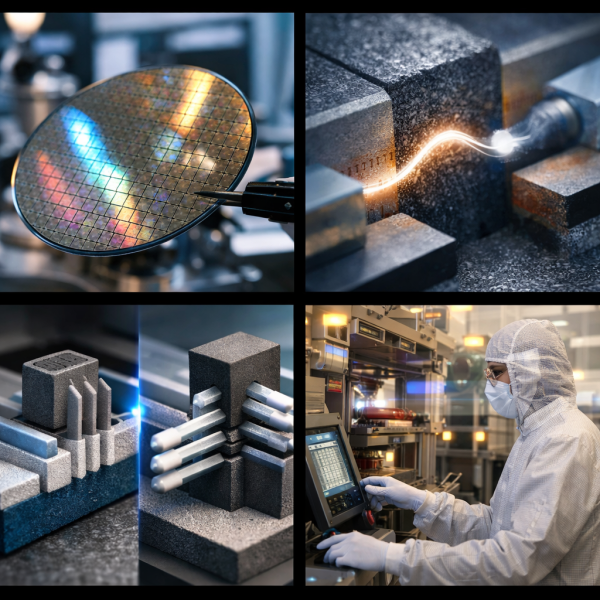

최근 3nm, 2nm 공정 이야기가 쏟아지고 있어요. 스마트폰 발표 행사에서 “더 작아진 칩, 더 강력한 성능”이라는 멘트는 이제 공식처럼 들립니다. 그런데 실제로 칩 설계를 들여다보면 상황이 그렇게 단순하지 않아요. 미세화가 극단으로 가면서, 우리가 상식적으로 이해하던 ‘전기 흐름’의 세계가 무너지기 시작했거든요. 🚀

칩이 작아질수록 무조건 좋아질 것 같지만, 트랜지스터 크기가 수 나노미터(10⁻⁹m) 수준으로 내려가면 전자는 더 이상 고전 물리학의 규칙만 따르지 않습니다. 이때부터는 양자역학이 개입해요. 전자는 벽을 ‘뚫고’ 지나가고, 꺼져 있어야 할 회로에서 미세한 전류가 흐르기 시작합니다. 이 글에서는 그 이상 현상이 왜 발생하는지, 그리고 산업이 어떻게 대응하고 있는지 깊이 있게 살펴보겠습니다. 🧠

🧠 트랜지스터의 원리: 스위치 하나가 세상을 움직인다

현대 반도체의 기본 단위는 트랜지스터입니다. 구조적으로 보면 게이트(Gate), 소스(Source), 드레인(Drain)으로 구성된 일종의 전자 스위치예요. 게이트에 전압을 가하면 전류가 흐르고, 전압을 차단하면 전류가 멈춥니다. 이 단순한 구조가 수십억 개 모여 CPU와 GPU를 구성하죠.

문제는 이 스위치를 계속 줄여왔다는 데 있어요. 90nm, 45nm, 7nm를 거쳐 이제는 3nm 이하까지 도달했습니다. 여기서 ‘nm’는 게이트 길이와 직접 일치하지는 않지만, 공정 세대의 상징적인 지표입니다. 더 작은 공간에 더 많은 트랜지스터를 넣기 위한 경쟁이었죠.

⚡ 반도체가 너무 작아지면 생기는 이상한 현상

미세화가 극단에 도달하면 다음과 같은 현상이 발생합니다.

1) 터널링 현상

전자가 절연막을 ‘뚫고’ 이동합니다. 원래는 전류가 차단되어야 하는 OFF 상태에서도 누설 전류(Leakage Current)가 발생해요.

2) 단채널 효과(Short Channel Effect)

채널 길이가 너무 짧아지면 게이트의 제어력이 약해집니다. 스위치를 꺼도 완전히 꺼지지 않는 문제가 생겨요.

3) 발열 증가

트랜지스터 밀도가 높아지면 전력 밀도도 증가합니다. 미세 누설 전류가 쌓이면 열로 변환되고, 이는 클럭 유지에 치명적입니다.

4) 변동성(Variability)

원자 단위 오차가 전체 성능에 영향을 줍니다. 공정 편차가 곧 수율 문제로 이어지죠.

이 지점에서 기존의 평면 구조는 한계에 부딪혔고, 산업은 구조 자체를 바꾸기 시작했습니다. 이 부분은 반도체 공정

🚀 그래서 등장한 FinFET과 GAA 구조

누설을 줄이기 위해 등장한 것이 FinFET 구조입니다. 채널을 지느러미(Fin) 형태로 세워 게이트가 3면을 감싸도록 설계했어요. 제어력을 강화하기 위한 선택이었죠.

그리고 3nm 이하에서는 GAA(Gate-All-Around) 구조가 도입됩니다. 이름 그대로 게이트가 채널을 완전히 둘러싸요. 전류 제어력을 극대화해 단채널 효과를 최소화하려는 설계입니다. 설계 철학이 “더 작게”에서 “더 입체적으로”로 전환된 순간이에요.

흥미로운 점은, 이제 미세화는 단순히 면적을 줄이는 경쟁이 아니라 구조적 혁신 경쟁이 되었다는 겁니다. 이 흐름은 양자 컴퓨팅

💻 산업적 목적과 사용자에게 미치는 영향

기업이 이렇게까지 무리하면서 미세화를 추진하는 이유는 명확해요. 동일 면적에서 더 많은 연산 유닛을 넣고, AI 연산 효율을 극대화하기 위함입니다. 특히 AI 가속기, 모바일 AP, 데이터센터 CPU는 전력 대비 성능(PPA)이 절대적 지표입니다.

사용자 입장에서는 배터리 지속 시간 증가, 발열 감소, AI 기능 강화로 체감됩니다. 하지만 역설적으로 설계 난이도와 제조 비용이 폭증하면서, 칩 가격은 상승하고 제품 가격에도 영향을 줘요.

미세화는 물리학, 재료공학, 회로 설계가 동시에 한계를 시험받는 영역이에요. 단순히 “더 작게 만들자”는 접근이 아니라, “물리 법칙을 어떻게 우회할 것인가”의 문제로 진화했습니다.

🧠 기술은 어디까지 줄어들 수 있을까?

현재 연구 단계에서는 1nm 이하 영역까지 논의되고 있지만, 이쯤 되면 실리콘 기반 CMOS 구조 자체가 유지될 수 있을지 의문이에요. 새로운 소재(그래핀, 2D 반도체), 새로운 계산 방식이 필요할지도 모릅니다.

• 트랜지스터는 나노 단위에서 양자역학의 영향을 받습니다.

• 누설 전류와 발열은 구조 혁신으로 대응하고 있습니다.

• 미세화 경쟁은 이제 ‘크기’가 아니라 ‘설계 철학’의 경쟁입니다.

우리는 여전히 실리콘이라는 물질 위에 문명을 쌓고 있어요. 그런데 그 토대가 원자 단위에서 흔들리기 시작했다면, 다음 컴퓨팅 패러다임은 어떤 모습일까요? 💭

여러분은 반도체가 더 작아지는 것이 계속 가능하다고 보시나요, 아니면 완전히 다른 방식의 컴퓨팅으로 넘어갈 시점이라고 생각하시나요? 의견을 댓글로 남겨주세요.

#반도체미세공정 #3나노 #GAA구조 #양자터널링 #AI반도체